to the timing requirements of I2Se:

Other than the word clock, the phasing of the DV-414 signals looks good. Like I2S, they clock on their falling edges (notice how the bit clock falls just as the word clock rises).

The conventional way to invert a signal would be use an inverter like the 74HCT04. A 74HCT04 has a typical propagation delay of 6 nS at 5 VCC so some gates from it could be useable for inversion and/or delay. But how about this as an alternative: the Motorola driver chip MC10H352 has inverting and non inverting output to drive the line balanced. How about simply switching the inverting and non-inverting lines somewhere between the chip and the output connector? I've confirmed with DAC-3 designer Peter Schut that this approach should work.

(Note that the corresponding Motorola PECL receiver is the MC10H350.)

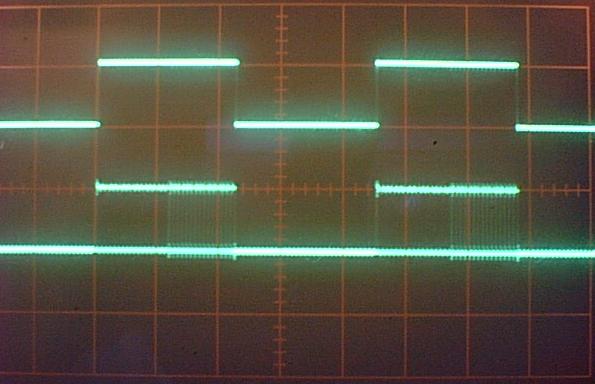

Combining the 44.1 k waveforms (word clock, bit clock, master clock,

from top to bottom):

to the timing requirements of I2Se:

Other than the word clock,

the phasing of the DV-414 signals looks good.

Like I2S, they clock on their falling edges

(notice how the bit clock falls just as the word clock rises).

One of the I2Se requirements is that the word and bit clocks need to be delayed 1-20 nS relative to the rising master clock. The signals above appear to just meet that spec.

However for 96 x 24 the timing becomes more critical and

the window narrows to 10 nS.

Combining the 96 kHz clocks below, they do seem to meet the 1-10 nS window.

(As in the combined 44k waveforms above, the 96k combination here

has word clock on top, bit clock middle, and master clock bottom.)

One other issue is that I2S data is left-justified (with a 1 bit clock delay from the word clock) whereas the DV-414 is right-justified. (The DV-414 signal format appears to follow the Sony/Burr-Brown standard.) If this is critical to I2S, there may be no simple way to get I2Se outputs from the DV-414. You could put a CS 8414 reciever and associated PLL into the DVD player, but that complexity belongs better on the receiver side in the external DAC. The best approach would probably be to add the second, high precision PLL to the receiver in the DAC, as Peter is doing for a future revision of the DAC-3 digital board.